Introduction aux Aspects Bas Niveau en Architecture des Systèmes Informatiques

Ce cours explore les mécanismes fondamentaux de l’architecture informatique, détaillant le rôle du CPU, de la mémoire, et des buses, pour comprendre comment ces éléments interagissent de manière optimisée, formant le socle des systèmes modernes.

Préambule

Dans cette introduction, nous allons nous concentrer sur les fondements bas niveau essentiels de l'architecture des systèmes informatiques.

Bien que l’on pourrait approfondir en explorant des sphères plus ardues – telles que la programmation directe des processeurs – notre dessein ici est de poser les assises conceptuelles indispensables.

Certains y verront l'occasion de consolider des savoirs déjà esquissés, tandis que d’autres découvriront, pour la première fois, les rouages fondamentaux qui soutiennent l'architecture des systèmes.

Ce cours sur l'architecture des systèmes informatiques explore la manière dont les composants matériels, logiciels et réseaux interagissent pour former un environnement fonctionnel et cohérent.

Objectifs

Nous allons :

- Explorer les composants essentiels qui constituent le cœur d’un processeur et d’une machine.

- Disséquer les principes de fonctionnement de chaque élément, afin de saisir comment ces composants interagissent en une parfaite symphonie.

Cette introduction vous dotera d’une compréhension solide des éléments constitutifs d’un système, établissant ainsi les fondations indispensables de l'architecture des systèmes.

En maîtrisant ces fondements, vous développerez une compréhension approfondie des mécanismes sous-jacents qui régissent le fonctionnement des systèmes informatiques. Ces connaissances vous prépareront à aborder des sujets techniques avancés, tels que la gestion de la mémoire en C, la programmation bas niveau, ou l’analyse de vulnérabilités. Ainsi, l'architecture des systèmes informatiques devient un socle essentiel pour quiconque souhaite exceller dans des domaines plus spécialisés et techniques.

Introduction

Définition de l’Architecture des Systèmes

Définition : Ensemble d'éléments interconnectés pour former une structure globale, organisée et fonctionnelle, où chaque composant remplit un rôle précis dans la cohésion globale de la machine.

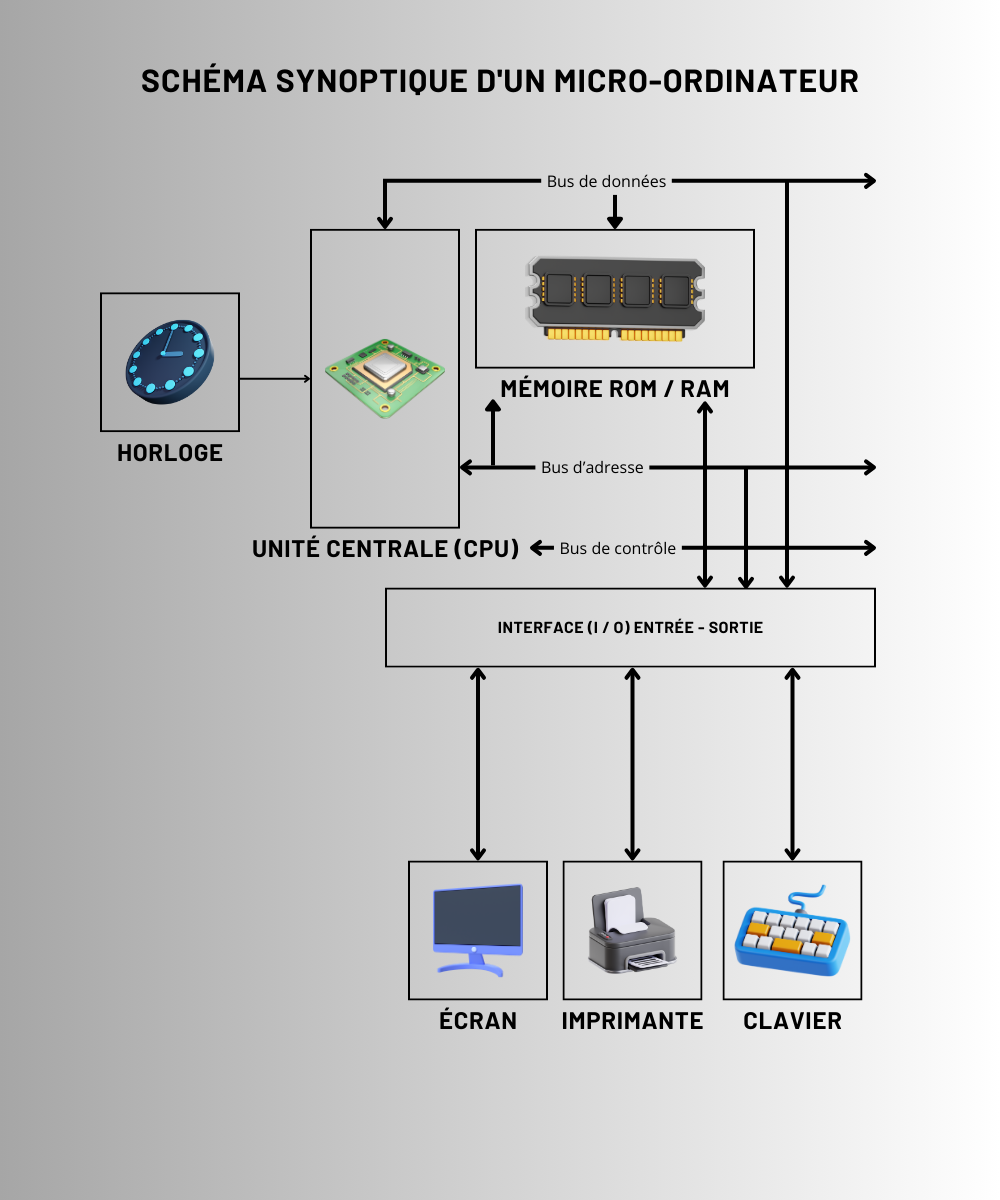

Vue Schématique d'une Machine

Une machine informatique est constituée de nombreux composants, mais elle peut être schématiquement représentée par un processeur central (CPU), dont l'exécution des instructions est régulée par une horloge interne.

Cette horloge envoie des impulsions régulières (appelées cycles d'horloge), qui déterminent la fréquence à laquelle le CPU exécute chaque étape d'instruction. Grâce à cette cadence, le CPU traite les données et les commandes en parfaite synchronisation avec les autres composants du système.

Pour bien saisir cette organisation, examinons chaque composant clé et son rôle dans le fonctionnement global de la machine :

1. Le Processeur (CPU) et les Instructions

Le CPU (Central Processing Unit) peut être comparé au cerveau de la machine, car il exécute les instructions fondamentales qui composent chaque programme. Ces instructions sont des ordres élémentaires que le CPU décode et traite en suivant une séquence précise. Elles incluent des types d'opérations variées, telles que :

- Opérations arithmétiques : addition, soustraction, multiplication, division, nécessaires aux calculs mathématiques de base.

- Opérations logiques : ET, OU, NON, qui permettent au CPU de prendre des décisions conditionnelles en comparant des valeurs.

- Déplacements de données : transfert de données entre les registres internes, la mémoire ou les périphériques, facilitant l'échange d'informations dans le système.

Chaque instruction est composée de plusieurs étapes, que le CPU exécute séquentiellement, de manière ordonnée et rapide. Par exemple, une instruction d'addition pourrait nécessiter une étape pour charger les données, une autre pour exécuter l'opération, et une dernière pour enregistrer le résultat.

Dans cet exemple :

- Chargement des données : Le CPU récupère les valeurs à traiter, soit depuis un registre interne, soit depuis la mémoire principale.

- Registres internes : Ce sont des mémoires de très faible capacité mais extrêmement rapides, situées directement dans le CPU. Ils stockent temporairement des données et des résultats intermédiaires pour les calculs en cours.

- Mémoire principale : Si les données ne se trouvent pas dans les registres, le CPU accède à la mémoire principale (RAM), qui est plus lente mais contient davantage de données.

- Exécution de l'opération : L’addition est effectuée par l’Unité Arithmétique et Logique (ALU).

- ALU (Unité Arithmétique et Logique) : L'ALU est une composante du CPU spécialisée dans les opérations de calcul. Elle effectue les opérations arithmétiques (comme l'addition et la multiplication) et les opérations logiques (comme les comparaisons). Pour une addition, l'ALU utilise des circuits logiques spécifiques appelés additionneurs, qui additionnent les bits des valeurs binaires en tenant compte des retenues.

- Stockage du résultat : Le résultat est enregistré pour un usage ultérieur.

- Registre interne : Si le résultat doit être réutilisé immédiatement, il est stocké dans un registre.

- Mémoire : Si le résultat doit être conservé plus longtemps, il est transféré vers la mémoire principale pour un accès ultérieur.

De manière plus précise et approfondie, voici comment chaque étape se déroule en détail :

Étape 1 : Chargement des Données

- Décodage de l'instruction : Lorsqu'une instruction est reçue par le CPU, l'unité de contrôle (CU), sous-système du CPU, la décode en interprétant sa séquence binaire (composée de 0 et de 1). Ce décodage permet de déterminer la nature de l'instruction et de comprendre l'opération à effectuer (par exemple, une addition) et d’identifier les registres ou emplacements mémoire nécessaires pour exécuter l’opération. Ce décodage utilise des décodeurs qui associent la séquence binaire à l'instruction correspondante.

- Fonction de la CU : L’unité de contrôle agit comme un chef d'orchestre, en coordonnant les opérations du CPU. Elle interprète les instructions et détermine le type d’opération (arithmétique, logique, ou transfert de données) et sélectionne les registres ou emplacements mémoire nécessaires pour l’exécution de l’instruction.

- Génération de signaux de contrôle : La CU envoie des signaux de contrôle (transmis par le bus de contrôle) pour synchroniser les opérations. Par exemple, elle peut indiquer à l'ALU quand commencer une opération ou à un registre d’enregistrer une valeur. Ces signaux, cadencés par l’horloge, orchestrent chaque étape.

- Récupération des valeurs : Une fois l’instruction décodée, la CU dirige le CPU pour charger les données requises depuis les registres internes ou la mémoire principale (RAM).

- Registres (internes) : Situés dans le CPU, les registres internes sont des mémoires ultra-rapides de très faible capacité (généralement quelques octets), conçues pour stocker temporairement les données immédiatement nécessaires aux calculs. Leur proximité avec l’ALU et la CU permet d’exécuter des opérations en un minimum de cycles d'horloge, assurant un accès quasi instantané aux données.

- Mémoire principale (RAM) : Lorsque les données nécessaires ne se trouvent pas dans les registres, la CU (Unité de Contrôle) utilise le bus d'adresse pour localiser et adresser les données dans la RAM. Une fois l'adresse définie, les données sont transférées au CPU via le bus de données. Bien que la RAM offre un stockage de grande capacité, elle est plus éloignée du CPU, et chaque accès prend généralement plusieurs cycles d'horloge, ce qui la rend plus lente que les registres pour les calculs immédiats.

Étape 2 : Exécution de l'Opération par l'ALU

L'Unité Arithmétique et Logique (ALU), une sous-composante du CPU, exécute les calculs nécessaires à l'instruction.

Qu’est-ce que l’ALU ? : L'ALU est spécialisée dans deux types d'opérations principales :

- Opérations arithmétiques : telles que l'addition, la soustraction, la multiplication, et parfois la division, qui permettent de traiter les calculs mathématiques de base.

- Opérations logiques : telles que les opérations ET, OU, NON, et les comparaisons de valeurs, qui sont essentielles pour la prise de décision conditionnelle et l'exécution des instructions logiques

Fonctionnement de l’ALU : Une fois les données chargées dans les registres appropriés et prêtes pour le traitement, l’ALU exécute l'opération en utilisant des circuits logiques spécifiques.

Par exemple, pour une addition, l’ALU utilise un circuit appelé additionneur qui additionne les bits correspondants de chaque valeur. Les additionneurs prennent en compte les retenues binaires, permettant des calculs précis en binaire.

Signalisation et Contrôle

- Transmission des signaux de commande via le bus de contrôle : Par analogie, on peut comparer l'unité de contrôle (CU) au chef d'orchestre du CPU, et le bus de contrôle aux veines ou canaux de transmission par lesquels circulent les instructions de ce chef d'orchestre vers les différents instruments (comme l'ALU et les registres). L'ALU reçoit ainsi des signaux de contrôle provenant de la CU, qui indiquent quelle opération spécifique doit être exécutée sur les données dans les registres. Ces signaux, transmis via le bus de contrôle, permettent à la CU d'envoyer des commandes précises, comme déclencher une addition ou un transfert de données, en activant les circuits logiques adéquats pour l’opération.

- Rôle du bus de contrôle : Le bus de contrôle est un ensemble de lignes de communication internes au CPU, dédiées à la transmission de signaux de commande et de synchronisation. Ce bus joue un rôle crucial dans la coordination des actions entre les différentes unités du CPU (comme l'ALU et les registres) et les autres composants du système (tels que la mémoire et les périphériques). Voici ses principales fonctions :

- Signalisation de commande : Les signaux comme "Lire" ou "Écrire" indiquent aux composants s'ils doivent lire des données dans la mémoire ou écrire un résultat.

- Synchronisation des opérations : En s’alignant sur l’horloge du CPU, le bus de contrôle garantit que chaque unité exécute ses opérations au moment précis requis, un peu comme un chef d'orchestre synchronisant chaque instrument pour une harmonie parfaite.

- Gestion des accès : Lors de demandes d’accès concurrentes (par exemple, vers la mémoire), le bus de contrôle organise et priorise les commandes pour éviter les conflits.

Étape 3 : Stockage du Résultat

- Enregistrement temporaire dans l’Accumulateur (AC) ou un registre interne : Une fois le calcul effectué par l'ALU (Unité Arithmétique et Logique), le résultat est souvent stocké temporairement dans un registre dédié. Dans certaines architectures, ce registre est l'accumulateur (AC), un registre spécifique conçu pour conserver les résultats intermédiaires et optimiser la rapidité des calculs en chaîne, notamment pour les opérations répétées ou successives. Dans des architectures plus avancées ou disposant de plusieurs registres polyvalents, le résultat peut être stocké dans un autre registre interne, offrant également un accès rapide pour des opérations immédiates ou des calculs supplémentaires dans le flux d'instructions.

- Rôle de l'AC (Accumulateur) : L'AC est un registre spécial utilisé pour stocker temporairement les résultats intermédiaires générés par l'ALU. Si une instruction implique des calculs successifs, l'AC conserve ces résultats partiels pour les étapes suivantes, permettant ainsi un accès rapide et évitant des allers-retours fréquents vers la mémoire principale. Cette fonctionnalité optimise la vitesse d'exécution, en particulier pour les opérations en chaîne.

- Transfert vers la mémoire principale (RAM) : Si le résultat doit être conservé pour une utilisation prolongée (conservé plus longtemps pour des besoins futurs dans le programme), il est transféré vers la mémoire principale (RAM) pour un accès ultérieur. Ce transfert est orchestré par l’unité de contrôle (CU), qui utilise deux bus distincts pour acheminer les informations de manière ordonnée : le bus d’adresse et le bus de données.

- Bus d’adresse : Le bus d’adresse peut être comparé à un GPS qui donne précisément l’emplacement où les données doivent être stockées en mémoire. La CU envoie d’abord l’adresse mémoire via le bus d’adresse, ce qui détermine l’emplacement exact en mémoire où le résultat doit être stocké. Ce bus transporte exclusivement des informations d’adresse, c’est-à-dire les coordonnées précises de la destination en mémoire. L’envoi de l’adresse est essentiel pour cibler la bonne position dans la RAM, garantissant que les données seront accessibles rapidement et de manière fiable lors d'une prochaine utilisation.

- Bus de données : Une fois l’adresse définie par le bus d’adresse, le bus de données prend le relais en acheminant la valeur des données – ici, le résultat du calcul – vers l’emplacement en mémoire préalablement ciblé. Le bus de données agit comme une autoroute pour le transfert du contenu, transportant les données depuis le CPU jusqu'à la mémoire.

Tandis que le bus d’adresse définit « où » les données doivent aller, le bus de données transporte « quoi » exactement doit être envoyé à cet emplacement.

Impact des cycles d'horloge : Ce processus de transfert prend plusieurs cycles d'horloge pour être exécuté. En effet, l’accès à la mémoire principale est plus lent que l’accès aux registres internes du CPU. Chaque étape (envoi de l’adresse, puis transfert des données) est synchronisée avec l’horloge du CPU, garantissant que chaque action se déroule au bon moment. Ce décalage dû au temps d’accès à la RAM constitue une latence, que le CPU doit compenser, en optimisant les accès mémoire autant que possible.

Ce processus séquentiel permet au CPU de décomposer chaque instruction en étapes précises, garantissant un flux d’opérations ordonné et une synchronisation parfaite avec les autres composants.

Ce processus séquentiel permet au CPU de décomposer chaque instruction en étapes bien définies, assurant un flux d’opérations ordonné et une synchronisation parfaite avec les autres composants. L’horloge interne rythme chaque étape, assurant que les opérations – décodage, chargement, calcul et stockage – se déroulent de manière fluide et efficace.

TL;DR

Le CPU, comparable au cerveau de la machine, décompose chaque instruction en étapes séquentielles, orchestrées par l'unité de contrôle (CU) et rythmées par l'horloge interne.

Fonctionnement général :

- Chargement des données :

- Les valeurs sont récupérées depuis des registres internes (rapides) ou la RAM (plus lente).

- Exécution des opérations :

- Réalisées par l'ALU pour des calculs arithmétiques ou logiques.

- Stockage des résultats :

- Résultats enregistrés dans l'accumulateur (AC) ou un registre interne, avant un éventuel transfert vers la RAM.

Rôles des Bus :

- Bus d'adresse : Indique où les données doivent être lues ou écrites.

- Bus de données : Transporte les informations.

- Bus de contrôle : Coordonne les actions (lire, écrire, exécuter).

Synchronisation et Performance :

- Chaque étape est synchronisée avec le signal d'horloge, garantissant un flux ordonné et efficace.

- La mémoire est plus lente que le CPU (les caches et le TLB optimisent l'accès en réduisant la latence).

Ce processus assure une exécution fluide des instructions, du chargement initial au stockage final, tout en coordonnant efficacement les interactions avec la mémoire et les périphériques.

2. Synchronisation par l'Horloge Interne

L'horloge interne du processeur, souvent comparée au cœur du système, est généralement un oscillateur à quartz. Cet oscillateur produit un signal d'horloge stable, mesuré en Hertz (Hz), qui définit la cadence à laquelle le système fonctionne. Ce signal d’horloge, génère une série d'impulsions électriques régulières – une onde carrée – qui établit la cadence du système. Ce signal établit une référence temporelle et crée une structure rythmique pour toutes les opérations du CPU et des autres composants (structurant et coordonnant le flux des opérations).

Qu'est-ce qu'un Oscillateur et son Rôle dans l'Horloge Interne ?

Un oscillateur est un composant électronique qui produit un signal périodique en générant des impulsions électriques régulières. Dans un système informatique, l'oscillateur est souvent réalisé à partir d’un cristal de quartz, connu pour ses propriétés de stabilité et de précision. Son rôle est de fournir un signal d'horloge fiable qui sert de référence temporelle pour coordonner toutes les opérations au sein du CPU et des autres composants.

Fonctionnement de l'Oscillateur à Quartz

L’oscillateur à quartz repose sur les propriétés piézoélectriques du quartz : lorsqu'une tension électrique est appliquée au cristal, il commence à vibrer à une fréquence spécifique. Ces vibrations naturelles génèrent un signal électrique périodique, qui oscille de manière stable et prévisible, créant ainsi un signal d'horloge sous forme d'une onde carrée.

- Ondes carrées : Les impulsions générées par le quartz produisent un signal d’horloge en forme d'onde carrée, composée d’un cycle "haut" (1) et d’un cycle "bas" (0). Ce cycle régulier, mesuré en Hertz (Hz), correspond à la fréquence d’horloge du système.

- Fréquence stable : Le quartz oscille à une fréquence très stable, qui ne varie pas ou très peu sous l’effet de la température ou de l’usure. Cette stabilité est cruciale pour garantir la fiabilité temporelle des opérations dans le CPU et les autres composants.

Par analogie :

- L’horloge agit comme le cœur de la machine, envoyant des impulsions régulières (les cycles d'horloge) qui battent le rythme du système.

- Le CPU est le cerveau, responsable du traitement des informations et de la prise de décisions en exécutant les instructions.

- L'unité de contrôle (CU) est le chef d'orchestre, coordonnant chaque étape des instructions en se synchronisant avec le battement de l'horloge.

- Les bus (d'adresse, de données et de contrôle) sont les veines, transportant les instructions et les données entre le CPU et les autres composants, comme la mémoire et les périphériques.

L’horloge impose ainsi un rythme uniforme qui synchronise chaque élément, permettant une transmission fluide et ordonnée des informations à travers le système. En cadencant chaque étape des opérations, l’horloge assure que chaque composant (le CPU, la mémoire, les bus et les périphériques) agit dans des fenêtres de temps définies, appelées cycles d'horloge. Ce rythme garantit que les données sont traitées, transférées et stockées de manière parfaitement ordonnée, évitant les conflits d’accès ou les transmissions hors séquence qui pourraient provoquer des erreurs.

En imposant cette cadence fixe, l’horloge optimise également les performances du système en limitant les temps morts et en réduisant les interruptions, permettant au CPU de travailler au maximum de sa capacité. La synchronisation précise aide aussi à minimiser les latences lorsque le CPU interagit avec des composants plus lents, comme la mémoire, en organisant les échanges de manière cohérente et efficace.

Cycle d’horloge : Chaque impulsion du signal d'horloge correspond à un cycle d'horloge, durant lequel le CPU effectue une étape spécifique d'instruction, comme charger des données, décoder une commande, ou exécuter une opération. La fréquence de l'horloge, mesurée en Hertz (Hz), indique le nombre de cycles effectués par seconde. Par exemple, une fréquence de 3 GHz signifie que le CPU peut traiter jusqu'à 3 milliards de cycles par seconde. Cette fréquence fixe la vitesse à laquelle le CPU peut progresser dans les instructions, chaque cycle représentant une unité temporelle où les composants du CPU agissent en synchronisation.

Synchronisation des composants : Ce battement régulier, généré par l'horloge, synchronise les actions du CPU avec celles des autres composants, de manière analogue à la distribution coordonnée du sang par le cœur dans un organisme. Chaque composant – mémoire, bus, périphériques – suit le rythme imposé par l'horloge, garantissant une transmission des données ordonnée et fluide. En agissant comme une pulsation synchronisatrice, l'horloge établit un rythme commun pour tous les éléments du système, alignant chaque étape d'instruction, de transfert de données et d’accès à la mémoire sur des cycles précis. Cette synchronisation étroite réduit les risques de conflits d'accès et d'interférences dans le flux d'instructions, minimisant les erreurs de transmission et optimisant la réactivité et la performance globale du système.

Contrôle par l'Unité de Contrôle (CU) : L’unité de contrôle (CU), véritable chef d'orchestre du système, utilise le signal d'horloge pour orchestrer les différentes phases d'instruction. En se synchronisant avec chaque cycle d'horloge, la CU cadence précisément chaque étape du processus – du décodage au chargement, en passant par le calcul et le stockage.

Pourquoi le Quartz ?

Le quartz est choisi comme matériau principal pour l’oscillateur d'horloge en raison de ses propriétés uniques, notamment sa piézoélectricité, qui en font un matériau idéal pour générer un signal d'horloge stable et précis.

- Propriétés Piézoélectriques : Le quartz présente des propriétés piézoélectriques, c’est-à-dire qu’il vibre naturellement à une fréquence stable lorsqu'il est soumis à une tension électrique. Ces vibrations produisent des impulsions électriques régulières, formant un signal d'horloge constant et fiable, essentiel pour maintenir la fréquence du système.

- Stabilité de Fréquence : Le quartz est très peu sensible aux variations de température, ce qui en fait un matériau particulièrement stable. Contrairement à d’autres matériaux qui peuvent se dilater ou se contracter, il conserve une fréquence d’oscillation constante, garantissant une cadence régulière même dans des conditions de fonctionnement variables.

- Précision et Durabilité : Le quartz peut être taillé pour vibrer à des fréquences très spécifiques, comme 32 kHz ou plusieurs mégahertz, selon les exigences du système. Cette précision, associée à une faible usure au fil du temps, rend le quartz particulièrement fiable pour une utilisation continue dans les systèmes informatiques.

Choix et Configuration de la Fréquence d’Horloge

1. Fréquence d'Horloge et Position de l'Oscillateur

L’oscillateur d'horloge se trouve généralement sur la carte mère et non à l'intérieur du CPU. Cet oscillateur génère le signal d'horloge pour synchroniser le CPU et les autres composants du système. Cependant, la fréquence finale du CPU est souvent une multiplication de la fréquence fournie par l'oscillateur de la carte mère. Par exemple, l'oscillateur peut générer une fréquence de base de 100 MHz, mais le CPU utilise un multiplicateur interne pour atteindre une fréquence de fonctionnement de 3 GHz.

2. Détermination et Adaptation de la Fréquence du CPU

Compatibilité et Communication entre le CPU et la Carte Mère via le BIOS/UEFI

Lorsqu’un CPU (par exemple, un Intel Core i5) est inséré dans une carte mère compatible, plusieurs étapes permettent de configurer la fréquence :

Le BIOS (Basic Input/Output System) et son successeur, l'UEFI (Unified Extensible Firmware Interface), sont des interfaces logicielles de bas niveau qui facilitent l’échange d’informations entre le CPU et la carte mère. Ces interfaces, stockées sur une puce dédiée sur la carte mère, jouent un rôle central dans la détection des composants et la configuration du système avant le démarrage de l’OS.

- Types d’Informations Échangées entre le CPU et le BIOS/UEFI

Lors de la mise sous tension, le BIOS/UEFI collecte des informations clés sur le CPU et d’autres composants matériels pour configurer le système de manière optimale. Les types d’informations échangées comprennent :

- Modèle et Architecture du CPU : Le BIOS/UEFI interroge le CPU pour connaître son modèle exact (par exemple, Intel Core i5-11400), son architecture (x86, x64), et ses capacités.

- Fréquence de Base et Multiplicateur : Ces paramètres déterminent la fréquence finale du CPU. La fréquence de base est la fréquence d'horloge initiale fournie par l'oscillateur de la carte mère, tandis que le multiplicateur est un coefficient appliqué par le CPU pour atteindre sa fréquence de fonctionnement.

- Limites de Consommation et Température Maximale : Ces limites (par exemple, la puissance thermique nominale ou TDP) permettent au BIOS/UEFI d'ajuster les paramètres d'alimentation et de refroidissement du CPU.

- Instructions Supportées : Le BIOS/UEFI identifie les ensembles d'instructions spécifiques (comme SSE, AVX) que le CPU est capable d’exécuter, ce qui peut affecter la compatibilité avec certains logiciels.

- Comment les Informations sont Échangées : Protocoles et Format de Communication

- Instruction CPUID : L’échange d’informations entre le CPU et le BIOS/UEFI utilise l’instruction spéciale CPUID. Lorsqu'elle est appelée, cette instruction renvoie une série de valeurs binaires codées qui décrivent les caractéristiques du CPU, comme le modèle, la fréquence maximale, et les capacités thermiques. Les données sont renvoyées dans des registres du CPU, chaque bit représentant un paramètre spécifique.

- Bus de Communication : Le CPU et le BIOS/UEFI communiquent via les bus internes de la carte mère, notamment le bus de contrôle et le bus de données. Le bus de contrôle détermine les signaux d'accès, comme « Lire » et « Écrire », tandis que le bus de données transfère les valeurs binaires échangées entre le CPU et la mémoire (RAM) ou le BIOS/UEFI.

- Horloge et Synchronisation : L’échange d’informations est cadencé par l’horloge système. Chaque cycle d'horloge synchronise les lectures et les écritures des données échangées entre le CPU et le BIOS/UEFI, garantissant une transmission des informations précise et sans conflits.

- Comment le BIOS/UEFI Détecte et Configure le CPU

- Lecture des Informations CPUID : Lorsque le BIOS/UEFI exécute la commande CPUID, il reçoit les informations brutes du CPU sous forme de codes binaires. Ces codes sont décodés pour identifier les spécifications, comme le modèle du processeur et les paramètres de fréquence.

- Configuration de la Fréquence et du Multiplicateur : Une fois les caractéristiques détectées, le BIOS/UEFI configure la fréquence d'horloge en fonction de la fréquence de base fournie par l'oscillateur de la carte mère. Le multiplicateur est alors appliqué pour atteindre la fréquence finale. Par exemple, une fréquence de base de 100 MHz avec un multiplicateur de 30 donne une fréquence CPU de 3 GHz.

- Contrôle de la Consommation : En fonction des limites thermiques et de consommation (ex. TDP) du CPU, le BIOS/UEFI ajuste les paramètres d’alimentation et peut activer des modes d’économie d’énergie, comme le mode Turbo Boost (pour augmenter temporairement la fréquence) ou le mode Idle (pour réduire la consommation lorsque le CPU est peu sollicité).

- Format et Décodage des Informations

- Valeurs Codées en Binaire : Les informations sont généralement codées en binaire, chaque bit représentant un état ou une caractéristique du CPU. Par exemple, un bit activé (1) peut indiquer que le CPU prend en charge un certain ensemble d'instructions, tandis qu’un bit désactivé (0) indiquerait le contraire.

- Registres : Les données renvoyées par le CPU sont stockées dans ses registres (petites unités de stockage à l'intérieur du CPU). Le BIOS/UEFI accède à ces registres pour lire et interpréter les valeurs, les convertissant en paramètres lisibles pour configurer le système.

- Stockage et Ajustement des Paramètres

- Sauvegarde dans le CMOS : Les paramètres détectés et configurés sont sauvegardés dans une mémoire non volatile, souvent appelée CMOS. Cette mémoire conserve les paramètres du BIOS même après l’extinction du système.

- Mise à Jour et Personnalisation : En accédant à l'interface du BIOS/UEFI (via des touches comme F2, F10 ou Delete), l'utilisateur peut ajuster manuellement certains paramètres, comme le multiplicateur pour l'overclocking, la limite thermique, ou les réglages de gestion de l’énergie.

En résumé, le BIOS/UEFI et le CPU échangent des informations cruciales pour assurer une compatibilité et une performance optimales :

- Types d’informations : Fréquence de base, multiplicateur, limites thermiques, et ensemble d'instructions.

- Protocoles et format : Utilisation de l’instruction CPUID et des bus de données/contrôle pour transférer les données en binaire.

- Rôle de l'horloge : Cadence le processus pour assurer une communication synchronisée.

- Paramètres de stockage : Les données sont conservées dans le CMOS pour une configuration persistante.

Cette architecture d'échange d'informations permet au BIOS/UEFI de configurer et de calibrer le CPU, garantissant ainsi une performance stable et adaptée au système d'exploitation et aux autres composants.

BIOS/UEFI : Interface de Bas Niveau pour la Configuration du Système

Le BIOS (Basic Input/Output System) et l'UEFI (Unified Extensible Firmware Interface) sont des interfaces logicielles de bas niveau stockées sur une puce de la carte mère. Ces interfaces jouent un rôle essentiel dans la gestion et la configuration du matériel lors de la mise sous tension du système.

- Qu’est-ce que le BIOS et l’UEFI ?

- BIOS : Traditionnellement, le BIOS est un programme intégré dans une puce de la carte mère, chargé de démarrer le système. Il initialise le matériel et charge ensuite le système d’exploitation (OS). Le BIOS fonctionne en mode 16 bits et est limité en fonctionnalités avancées, ce qui l’a rendu progressivement obsolète pour les besoins modernes.

- UEFI : Remplaçant du BIOS classique, l'UEFI est une interface plus avancée, fonctionnant en 32 ou 64 bits. Il supporte des interfaces graphiques, la gestion de disques plus grands, et une sécurité accrue (comme Secure Boot). L’UEFI est devenu le standard dans les systèmes modernes et est beaucoup plus rapide et flexible que le BIOS traditionnel.

- Rôle du BIOS/UEFI dans la Détection et l'Initialisation des Composants

Lors de la mise sous tension, le BIOS/UEFI effectue une série de tests et d’actions :

- Power-On Self Test (POST) : Le BIOS/UEFI effectue d’abord un test de démarrage (POST) pour s’assurer que les composants matériels, tels que la RAM, le CPU, la carte graphique et les périphériques de stockage, sont fonctionnels.

- Détection du CPU : Le BIOS/UEFI lit les informations sur le modèle et les spécifications du CPU via le CPUID, une instruction spécifique du CPU qui permet de communiquer ses caractéristiques (modèle, fréquence de base, multiplicateur, limites thermiques, etc.).

- Multiplicateur de fréquence : La fréquence d’horloge effective du CPU est obtenue en multipliant la fréquence de base (fourni par l'oscillateur de la carte mère) par un coefficient interne propre au CPU. Par exemple, si la fréquence de base est de 100 MHz et le CPU utilise un multiplicateur de 30, la fréquence finale est 3 GHz.

- Overclocking et Sous-cadencement : Certains processeurs et cartes mères permettent des ajustements manuels de ce multiplicateur pour overclocker (augmenter la fréquence au-delà de celle spécifiée) ou sous-cadencer (réduire la fréquence pour économiser l’énergie). Cette pratique peut modifier la performance et la consommation d’énergie, mais elle dépend des capacités de la carte mère et du modèle de CPU.

- Compatibilité entre le CPU et la Carte Mère

- Socket et Chipset : Le socket de la carte mère doit correspondre à celui du CPU. Par exemple, un processeur Intel Core i5-11400 utilise un socket LGA1200, il faut donc une carte mère avec ce même socket. Le chipset de la carte mère (un composant qui gère la communication entre le CPU et d'autres composants) doit également être compatible pour assurer le support des fonctionnalités du processeur.

- BIOS/UEFI Mise à Jour : Parfois, les nouvelles générations de CPU sont supportées par des cartes mères existantes, mais nécessitent une mise à jour du BIOS pour assurer une compatibilité totale.

- Mémoire (RAM) : La carte mère et le CPU imposent des limites sur la vitesse et le type de RAM compatibles (DDR4, DDR5, etc.). Vérifier la compatibilité de la mémoire est essentiel pour que le CPU fonctionne à sa pleine capacité.

L’Unified Extensible Firmware Interface (UEFI) est une spécification ouverte, établie par l’UEFI Forum, un consortium réunissant les grandes entreprises de l’industrie informatique. Elle définit une interface entre le micrologiciel (ou firmware) d’une carte mère et les logiciels, tels que le chargeur d'amorçage, le système d’exploitation, les applications et les pilotes.

Introduite progressivement à partir des années 2000 pour remplacer le BIOS sur les PC, l’UEFI a également trouvé sa place dans les systèmes embarqués. Contrairement au BIOS, qui est limité dans ses fonctionnalités, l’UEFI propose une interface de haut niveau, capable de gérer un système dès son démarrage. Elle offre une interaction directe avec les disques, le réseau, et les périphériques connectés. En outre, l’UEFI intègre une interface en ligne de commande, ainsi que des fonctions de dessin, permettant de concevoir une interface graphique plus conviviale pour l’utilisateur.

TL;DR

- Rôle de l'Horloge : L’horloge interne du CPU, souvent un oscillateur à quartz, produit un signal d'horloge stable (onde carrée) qui cadence les opérations du système. Ce signal synchronise le CPU, la mémoire et les périphériques pour garantir un flux ordonné et efficace des instructions.

- Cycle d’Horloge : Chaque cycle correspond à une étape d’exécution d’une instruction (charger, décoder, exécuter). La fréquence d’horloge, mesurée en Hertz (Hz), détermine le nombre de cycles traités par seconde (ex. : 3 GHz = 3 milliards de cycles/s).

- Communication CPU/Carte Mère : Le CPU utilise l’instruction CPUID pour communiquer ses spécifications (fréquence, limites thermiques, etc.) au BIOS/UEFI via des bus de contrôle et de données. Le BIOS configure alors la fréquence d’horloge en appliquant un multiplicateur à la fréquence de base.

- UEFI vs BIOS : L'UEFI remplace le BIOS en offrant des fonctionnalités avancées (interface graphique, gestion des disques modernes, sécurité accrue). Il initialise et configure les composants comme le CPU, la RAM et les périphériques.

- Compatibilité : Le CPU et la carte mère doivent être compatibles en termes de socket, chipset et fréquences supportées. Des mises à jour du BIOS/UEFI peuvent être nécessaires pour garantir cette compatibilité.

- Pourquoi le Quartz : Le quartz est choisi pour sa stabilité et sa précision. Il génère un signal fiable et constant, essentiel pour maintenir une synchronisation temporelle dans les systèmes informatiques.

3. Les Bus

Comme mentionné précédemment, le CPU est connecté à divers composants du système (mémoire, périphériques, etc.) via des bus. Ces bus jouent un rôle essentiel en permettant la communication et l'échange de données entre les différentes parties de la machine.

Qu’est-ce qu’un Bus ?

Un bus est un ensemble de lignes de communication (ou fils) par lesquelles transitent des signaux électriques représentant des données, des adresses ou des commandes. Chaque ligne du bus transporte un bit à la fois, et l’ensemble des lignes détermine le nombre de bits qui peuvent être transmis simultanément. Par exemple, un bus de 64 bits peut transférer 64 bits de données en un seul cycle.

- Structure physique : Les bus sont généralement intégrés à la carte mère et relient directement le CPU, la mémoire principale (RAM), et d’autres périphériques comme les disques durs ou les cartes graphiques.

- Cadence : La transmission des signaux est cadencée par l’horloge système. À chaque impulsion de l’horloge (ou cycle), les données sont envoyées par "rangées", ce qui détermine la fréquence d’envoi et donc la vitesse des échanges.

Rôles des Bus

Les bus sont divisés en plusieurs catégories, en fonction du type de données qu’ils transportent :

- Bus de Données :

- Transporte les données brutes entre le CPU et les autres composants.

- Par exemple, lors d'une opération de lecture, la mémoire transfère les données demandées via ce bus pour que le CPU les traite.

- Bus d’Adresse :

- Spécifie l’emplacement mémoire ou le périphérique cible pour une opération donnée.

- Lorsqu’une donnée doit être lue ou écrite, le CPU place l’adresse correspondante sur ce bus pour indiquer où effectuer l’opération.

- Bus de Contrôle :

- Transporte les commandes et signaux de synchronisation.

- Par exemple, des signaux comme « Lire », « Écrire » ou « Exécuter » sont envoyés via ce bus pour coordonner les actions.

La fréquence d'horloge, mesurée en Hertz (Hz), détermine la vitesse à laquelle les données sont envoyées via les bus. Plus la fréquence est élevée, plus les cycles d'horloge sont rapides, ce qui accélère la transmission des informations.

Exemple Pratique

Supposons qu’une instruction nécessite la lecture de données en mémoire :

- Bus d’Adresse : Le CPU envoie l'adresse mémoire de la donnée cible sur ce bus.

- Bus de Contrôle : Un signal « Lire » est envoyé pour indiquer que l'opération est une lecture.

- Bus de Données : Les données à l’adresse spécifiée sont renvoyées via ce bus au CPU.

Communication entre le CPU et la Mémoire : Rôle des Bus d'Adresse et de Données

L’un des rôles fondamentaux d’un système informatique est de permettre au CPU d’accéder à la mémoire principale (RAM) pour lire ou écrire des données. Cette interaction repose sur deux types de bus principaux : le bus d'adresse et le bus de données. Ces bus travaillent en coordination pour localiser les données en mémoire et assurer leur transfert.

1. Rôle du Bus d'Adresse

Le bus d’adresse sert à spécifier l’emplacement mémoire où une opération (lecture ou écriture) doit être effectuée. Le CPU utilise ce bus pour transmettre l’adresse mémoire ciblée :

- Spécification de l'adresse : L'adresse mémoire est formée dans le CPU et envoyée sur le bus d'adresse. Cela indique au composant mémoire (RAM) quel emplacement spécifique doit être utilisé.

- Un canal unidirectionnel : Le bus d’adresse est unidirectionnel, car les adresses sont toujours émises par le CPU vers la mémoire.

2. Rôle du Bus de Données

Le bus de données est responsable du transfert des données entre le CPU et la mémoire :

- Lecture des données : Lorsque le CPU demande une donnée, la mémoire envoie cette donnée au CPU via le bus de données.

- Écriture des données : Lorsqu’une instruction exige que le CPU écrive une donnée en mémoire, celle-ci est placée sur le bus de données, puis transférée à l’emplacement mémoire spécifié par le bus d’adresse.

- Un canal bidirectionnel : Contrairement au bus d'adresse, le bus de données est bidirectionnel, car les données peuvent circuler dans les deux sens (du CPU vers la mémoire et inversement).

3. Rôle du Bus de Contrôle

Le bus de contrôle est un canal de communication interne essentiel qui coordonne les échanges entre le CPU, la mémoire, et les périphériques. Ce bus transmet des signaux de commande et de synchronisation qui orchestrent les opérations du système.

Qu'est-ce que les Entrées/Sorties (I/O)

Les termes I/O (Input/Output) désignent tous les périphériques permettant d’échanger des données avec l’ordinateur. Cela inclut :

- Entrées : Claviers, souris, microphones, capteurs.

- Sorties : Écrans, imprimantes, haut-parleurs.

- Entrées/Sorties mixtes : Disques durs, cartes réseau, clés USB.

Les I/O fonctionnent en interaction avec le CPU, qui envoie et reçoit des instructions et des données pour traiter ou afficher des informations.

Rôle du Bus de Contrôle dans les I/O

Le bus de contrôle agit comme un chef d’orchestre pour les échanges avec les périphériques. Il ne transporte pas directement les données (rôle du bus de données) ni les adresses (rôle du bus d’adresse), mais il supervise les interactions et transmet des signaux de commande : Commandes spécifiques, des signaux comme « Lire », « Écrire », ou « Attente » informent les périphériques des actions à effectuer.

Synchronisation : Le bus de contrôle garantit que les périphériques opèrent en accord avec l’horloge du CPU, minimisant les conflits et assurant une exécution ordonnée des opérations.

La Mémoire : Un Périphérique Particulier

Bien que la mémoire principale (RAM) soit un élément central du système, elle est traitée comme un périphérique par le CPU. Le bus de contrôle joue un rôle clé dans la programmation et la gestion de la mémoire en collaboration avec la Memory Management Unit (MMU) :

Programmation via instructions machines :

- Le CPU utilise des instructions spécifiques pour configurer la mémoire.

- Définir les plages d’adresses accessibles.

- Spécifier les droits d’accès (lecture, écriture, exécution).

- Configurer les optimisations, comme les caches.

- Coordination des accès : Le bus de contrôle garantit que les accès mémoire s’effectuent sans conflit, même en cas de demandes simultanées.

Lien entre la MMU et le Bus de Contrôle

La Memory Management Unit (MMU) gère la traduction des adresses virtuelles en adresses physiques et utilise le bus de contrôle pour programmer et synchroniser ces opérations.

La Memory Management Unit (MMU) est un composant matériel intégré au processeur (ou à proximité immédiate) qui gère la traduction des adresses virtuelles en adresses physiques. Cette traduction est essentielle dans les systèmes modernes où la mémoire est partagée entre plusieurs processus, chacun ayant sa propre vue isolée de la mémoire (appelée espace d’adressage).

Pourquoi une MMU ?

La MMU remplit plusieurs fonctions critiques :

- Isolation des processus : Chaque programme voit un espace mémoire indépendant, ce qui empêche un processus d’accéder à la mémoire d’un autre.

- Gestion de la pagination : La mémoire est divisée en blocs appelés pages, facilitant la gestion et l’utilisation efficace de l’espace disponible.

- Optimisation des performances : La MMU réduit les frais liés aux traductions d’adresses grâce à des caches comme le TLB.

Fonctionnement de la MMU

- Traduction d’Adresses

Le CPU émet des adresses virtuelles lors de l’exécution d’instructions. La MMU convertit ces adresses virtuelles en adresses physiques en suivant une table de correspondance maintenue par le système d’exploitation. Voici comment cela fonctionne :

- Adresse Virtuelle : L’adresse émise par le CPU est divisée en deux parties :

- Page Number : Identifie la page dans laquelle se trouve la donnée.

- Page Offset : Position exacte de la donnée dans la page.

- Recherche de la Page : La MMU consulte une table des pages pour trouver l’adresse physique correspondant au numéro de page.

- Adresse Physique : La MMU combine l’adresse physique de la page avec le décalage (offset) pour obtenir l’emplacement exact de la donnée dans la mémoire.

- Pagination et Mémoire Virtuelle

La MMU fonctionne avec un mécanisme appelé pagination, où la mémoire est divisée en blocs fixes de taille uniforme :

- Pages Virtuelles : Parties de l’espace mémoire virtuel.

- Frames Physiques : Équivalents des pages dans la mémoire physique. Une table des pages maintient la correspondance entre les pages virtuelles et les frames physiques.

Le Translation Lookaside Buffer (TLB) : Accélérateur de Traductions

La traduction d’adresses peut être lente si elle nécessite des consultations fréquentes dans la table des pages. Pour résoudre ce problème, la MMU utilise un Translation Lookaside Buffer (TLB), un cache dédié aux traductions d’adresses.

Fonctionnement du TLB

Le TLB stocke les traductions les plus récentes ou les plus fréquemment utilisées. Lorsqu’une adresse virtuelle est émise :

- La MMU vérifie d’abord le TLB pour voir si la traduction est déjà en cache.

- Hit : Si l’adresse est trouvée, la MMU utilise la traduction sans consulter la table des pages.

- Miss : Si l’adresse n’est pas trouvée, la MMU consulte la table des pages, met à jour le TLB, puis procède à la traduction.

Avantages du TLB

- Réduction de la latence : Les traductions via le TLB sont beaucoup plus rapides que via la table des pages.

- Optimisation des cycles d’horloge : En évitant des recherches coûteuses, le TLB améliore les performances globales du système.

Limites et Gestion du TLB

- Taille limitée : Le TLB ne peut stocker qu’un nombre restreint de traductions. Lorsqu’il est plein, de nouvelles traductions remplacent les plus anciennes (ou les moins utilisées).

- Flushing : Lors d’un changement de contexte (par exemple, changement de processus), le TLB doit être invalidé (flush) pour éviter des incohérences.

Interactions entre le CPU, la MMU, et le TLB

- Cycle d’Accès Mémoire

Lorsqu’une instruction requiert un accès mémoire :

- Le CPU génère une adresse virtuelle.

- La MMU intercepte cette adresse et consulte le TLB :

- Si la traduction est dans le TLB (hit), elle est utilisée directement.

- Sinon (miss), la MMU consulte la table des pages et met à jour le TLB.

Une fois l’adresse physique obtenue, la mémoire physique (RAM) est consultée pour récupérer ou écrire les données.

- Rôle du Bus de Contrôle

Le bus de contrôle intervient pour transmettre les commandes nécessaires à ces opérations :

- Commande "Lire" ou "Écrire" : Spécifie l’action à effectuer sur la mémoire.

- Coordination des cycles : Le bus de contrôle assure que la MMU, le CPU, et la mémoire opèrent en synchronisation.

Voici les principaux rôles de la MMU en relation avec le bus de contrôle :

- Définir les plages d’adresses virtuelles : Le CPU configure la MMU pour attribuer des adresses spécifiques à chaque processus.

- Optimiser avec le TLB : La MMU utilise le Translation Lookaside Buffer (TLB) pour stocker des traductions d’adresses récentes. Le TLB réduit la latence en évitant les recalculs lors d’un accès répété à une même adresse.

- Transmettre des signaux via le bus de contrôle : Les configurations, commandes, et synchronisations nécessaires à la MMU sont transmises par ce bus.

Interactions avec le Bus d’Adresse et le Bus de Données

Le bus de contrôle fonctionne en collaboration avec :

- Le Bus d’Adresse : Permet au CPU d’indiquer l’adresse mémoire ou l’emplacement du périphérique avec lequel il souhaite interagir.

- Le Bus de Données : Transporte les données entre le CPU, la mémoire et les périphériques, en suivant les commandes du bus de contrôle.

Processus Global : Lecture et Écriture en Mémoire

Voici un résumé des étapes typiques d’une interaction entre le CPU et la mémoire :

- Demande du CPU : Le CPU émet une instruction qui nécessite l’accès à la mémoire (lecture ou écriture).

- Adresse via le Bus d'Adresse : Le CPU place l’adresse mémoire cible sur le bus d'adresse pour spécifier l’emplacement.

- Commande via le Bus de Contrôle : Le CPU envoie un signal sur le bus de contrôle pour indiquer la nature de l’opération (lecture ou écriture).

- Transfert des Données :

- Pour une lecture, la mémoire place les données demandées sur le bus de données, et celles-ci sont transférées au CPU.

- Pour une écriture, le CPU place les données sur le bus de données, qui les envoie ensuite à la mémoire.

Stockage dans les Caches : Le CPU peut conserver une copie locale des données dans ses caches pour des opérations futures.

Coordination et Cache du CPU

Pour optimiser l’accès à la mémoire, le CPU utilise des mécanismes comme les caches internes et les buffers pour réduire les temps d'accès :

- Caches internes : Le CPU conserve une copie temporaire des données fréquemment utilisées dans des caches. Cela permet de réduire les allers-retours avec la mémoire principale, qui est plus lente.

- Rafraîchissement par paquets : Lorsque le CPU accède à la mémoire, il peut récupérer ou écrire des données par paquets (par exemple, des blocs de plusieurs octets). Cela permet d’optimiser l’utilisation des bus en réduisant le nombre de transactions nécessaires.

Les latences mémoire

Bien que ces opérations semblent instantanées, elles impliquent des délais appelés latences mémoire. Ces délais proviennent du temps nécessaire pour transmettre les adresses et les données, ainsi que de la synchronisation avec l’horloge. Les caches internes du CPU permettent de compenser ces latences en réduisant la dépendance directe à la mémoire principale.

Bien que les bus d’adresse et bus de données permettent une communication rapide entre le CPU et la mémoire, il existe une latence intrinsèque due à la différence de vitesse entre le CPU et la mémoire principale (RAM). Cette disparité est une contrainte majeure dans l’architecture des systèmes modernes.

TLDR

Les bus permettent la communication entre le CPU, la mémoire, et les périphériques en transportant des données, adresses, et commandes. Ils jouent un rôle central dans l'architecture d'un système informatique :

Types de Bus :

- Bus de Données : Transporte les données entre le CPU et les composants (bidirectionnel).

- Bus d'Adresse : Spécifie où effectuer une opération en mémoire (unidirectionnel).

- Bus de Contrôle : Coordonne les actions avec des signaux (ex. "Lire", "Écrire").

Processus typique d'accès mémoire :

- CPU demande une donnée :

- L’adresse cible est envoyée sur le bus d’adresse.

- Un signal "Lire" est émis via le bus de contrôle.

- Mémoire répond :

La donnée est transmise au CPU via le bus de données.

Optimisations :

- MMU (Memory Management Unit) : Traduit les adresses virtuelles en adresses physiques.

- TLB (Translation Lookaside Buffer) : Accélère les traductions d’adresses grâce à un cache dédié.

- Caches internes : Réduisent les latences en stockant localement les données fréquentes.

Points clés :

- Les bus travaillent en synchronisation avec l’horloge système.

- Les latences mémoire proviennent de la lenteur relative de la RAM par rapport au CPU, partiellement compensées par les caches.

4. Considérations de Latence

1. Une Perception Trompeuse : L’Illusion de Proximité (Transparence dans les Architectures Modernes)

Les architectures modernes et la programmation bas niveau sont conçues pour rendre les interactions avec la mémoire transparente pour les développeurs et utilisateurs. Cela signifie que, bien qu'un certain décalage temporel existe entre l'émission d'une instruction et son effet réel sur la mémoire, tout est orchestré pour que ce processus soit invisible et considéré comme immédiat :

- Instruction mémoire et hypothèse immédiate : Lorsqu'une instructionmachine effectue une opération sur la mémoire (écriture ou lecture), l’architecture et les outils logiciels font en sorte que le développeur puisse supposer que l’opération est instantanée et que la modification est déjà effective avant de passer à l’instruction

En pratique, des latences mémoire subsistent. Les données modifiées peuvent être temporairement stockées dans des buffers, des caches ou même être en cours de traitement avant d’atteindre leur destination finale. Ce mécanisme est invisible grâce à des stratégies comme les écritures différées (write-back) ou les transactions atomiques.

En effet, encore une fois, à première vue, les échanges entre le CPU et la mémoire semblent instantanés, car les signaux circulent à des vitesses proches de celles de la lumière. Cependant, à l’échelle des fréquences d’horloge du processeur, cette communication n'est pas immédiate :

- Distance apparente : Pour le CPU, accéder à la mémoire principale peut être perçu comme un échange avec un élément distant, même si la mémoire est physiquement proche sur la carte mère.

- Comparaison temporelle : Une opération d'accès à la mémoire prend plusieurs cycles d'horloge, alors que le CPU peut exécuter plusieurs instructions par cycle. Cette différence crée un décalage significatif entre la vitesse de traitement du CPU et la vitesse d’accès à la mémoire.

2. Une Magnitude Importante : La Différence de Fréquence

Le CPU moderne fonctionne à des fréquences de plusieurs gigahertz (GHz), ce qui correspond à des milliards de cycles par seconde. En revanche, la mémoire principale (même avec des technologies rapides comme la DDR4 ou DDR5) opère à des fréquences bien inférieures. Cette disparité se traduit par une magnitude de latence entre les deux :

- Temps d’accès mémoire : Accéder à un emplacement mémoire peut prendre des dizaines de cycles d'horloge CPU, ce qui ralentit l’exécution des instructions nécessitant des données non disponibles dans les caches internes.

- Comparaison analogique : Ce décalage peut être comparé à un câble réseau reliant deux points éloignés. Bien que le signal voyage rapidement, la transmission et le traitement prennent suffisamment de temps pour être perceptibles à l’échelle du processeur.

3. Conséquences des Latences Mémoire

La latence mémoire a des implications importantes sur les performances du système :

- Coût d'une opération d'entrée-sortie : L'accès à la mémoire principale est considéré comme une opération coûteuse, car elle implique plusieurs cycles d'horloge pour transférer les données entre le CPU et la RAM.

- Instructions non instantanées : Sur des architectures plus anciennes, une instruction nécessitant un accès mémoire pouvait être bloquée jusqu’à ce que l’opération de lecture ou d’écriture soit terminée. Cela signifiait que l’instruction suivante ne pouvait pas commencer immédiatement.

4. Mécanismes pour Réduire la Latence

Pour minimiser cet écart et améliorer les performances, plusieurs solutions ont été mises en œuvre dans les architectures modernes :

- Caches internes : Le CPU conserve une copie locale des données fréquemment utilisées dans des mémoires internes (L1, L2, L3). Les accès à ces caches sont beaucoup plus rapides que ceux à la mémoire principale.

- Préfabrication (Prefetching) : Le CPU anticipe les données qui seront nécessaires et les charge dans ses caches avant qu’elles ne soient explicitement demandées.

- Mémoire intercalée (Interleaving) : La mémoire est divisée en blocs accessibles simultanément, ce qui permet de traiter plusieurs demandes en parallèle.

5. Un Système en Harmonie Temporelle

Bien que les latences mémoire restent une contrainte, la synchronisation temporelle orchestrée par l’horloge système permet au CPU de coordonner ses opérations avec celles de la mémoire. Chaque étape (lecture, écriture) est cadencée pour garantir un fonctionnement fluide, malgré les disparités de vitesse.

Implications Critiques : La Subtilité des Échanges Mémoire

Dans la majorité des cas, cette transparence est acceptable. Cependant, dans des situations critiques, comme en sécurité ou en conception matérielle bas niveau, cette abstraction peut poser problème :

Attaques exploitant ces mécanismes :

- Les canaux auxiliaires (side-channel attacks) exploitent les temporels (latences, accès aux caches) pour extraire des données sensibles.

- Les techniques comme Rowhammer manipulent les accès mémoire pour provoquer des erreurs sur des données adjacentes, en contournant les abstractions prévues.

Précision requise dans l'ingénierie bas niveau :

- En ingénierie fonctionnelle, il est souvent acceptable de supposer que l’écriture en mémoire est immédiate.

- En conception critique (matérielle ou logicielle), cette hypothèse ne peut être faite. Les mécanismes sous-jacents, comme les optimisations des caches ou les transactions mémoire, doivent être explicitement pris en compte.

Sécurité et Programmation Bas Niveau

Le domaine de la sécurité informatique au niveau des processeurs et de la mémoire reste un champ de recherche fascinant et spécialisé. Les failles matérielles (comme Meltdown ou Spectre) illustrent comment l'exploitation des mécanismes internes du CPU peut compromettre des systèmes entiers :

- Comprendre le bas niveau : Les ingénieurs spécialisés en sécurité doivent maîtriser les subtilités des caches, des buffers et des mécanismes d’accès pour analyser et corriger ces vulnérabilités.

- Attaques basées sur l'abstraction : Les attaquants exploitent souvent l’écart entre ce que le système semble faire (transparence) et ce qu'il fait réellement.

Pour les passionnés du bas niveau, ce domaine offre des possibilités immenses, tant pour l'optimisation que pour la recherche en sécurité. Les concepts abstraits comme les caches et les bus deviennent des outils concrets à manipuler ou à analyser dans des contextes critiques.

TLDR

- Illusion de Proximité

- Les architectures modernes rendent les interactions CPU-mémoire transparentes : les écritures/lectures semblent instantanées.

- En réalité, des latences mémoire existent, avec des données souvent stockées temporairement dans des caches ou buffers avant d’atteindre leur destination.

- Écart de Fréquence

- Les CPU fonctionnent à plusieurs GHz, mais la mémoire (RAM) est plus lente, créant une latence de plusieurs cycles d’horloge.

- Comparaison : accéder à la mémoire, c’est comme communiquer via un câble réseau avec un élément distant.

- Impact des Latences Mémoire

- Accéder à la RAM est coûteux en cycles d’horloge.

- Une instruction dépendant de la mémoire peut bloquer l’exécution suivante, ralentissant le CPU.

- Optimisations pour Réduire la Latence

- Caches internes (L1, L2, L3) : stockage rapide des données fréquemment utilisées.

- Préfabrication (Prefetching) : anticipation des besoins en données.

- Mémoire intercalée : parallélisme dans l'accès à la mémoire.

- Applications Critiques

- En sécurité, des attaques (ex. Rowhammer, Spectre) exploitent ces latences.

- En programmation bas niveau, comprendre ces mécanismes est essentiel pour éviter les incohérences mémoire ou les failles.

Bien que la latence soit inévitable, les mécanismes de synchronisation orchestrés par l’horloge système permettent d’assurer un fonctionnement globalement fluide.

5. Principes des Caches : Accélération des Accès Mémoire

1. Rôle des Caches dans l’Accélération

Les caches mémoire jouent un rôle crucial dans l’architecture moderne des processeurs. Une fois configurés et activés, ils permettent de réduire considérablement la latence des accès mémoire. Plutôt que d'accéder directement à la mémoire principale (RAM), qui est beaucoup plus lente, le CPU peut taper dans le cache, où sont stockées temporairement les données les plus fréquemment ou récemment utilisées.

- Effet d’Accélération : Lorsqu'une donnée est déjà présente dans le cache, le CPU peut y accéder sans effectuer de requête vers la mémoire principale. Cela réduit le nombre d'opérations nécessaires et améliore les performances globales.

- Différence de Latence : Sans cache, accéder à la RAM peut prendre jusqu’à 1000 cycles d’horloge. Avec un cache bien configuré, ce délai peut être réduit à 50 cycles ou moins, selon la hiérarchie des caches (L1, L2, L3). Cependant, même avec des caches, ces accès ne sont pas instantanés et restent plus coûteux que l’accès direct aux registres internes.

2. La Mémoire Vue comme une Ressource Distante

Pour le CPU, la mémoire principale (RAM) est perçue comme une ressource externe et distante. Comparons cette situation à un scénario logistique :

- Mémoire distante : La RAM est comme un entrepôt situé dans un autre bâtiment. Accéder à une donnée implique un aller-retour coûteux.

- Caches locaux : Les caches sont des mini-entrepôts situés à proximité immédiate, permettant d’accéder plus rapidement aux données fréquemment utilisées.

Cette analogie illustre pourquoi la hiérarchie des caches est essentielle pour réduire les goulots d’étranglement liés aux latences mémoire.

3. Exigences de Performance et Hyper-Threading

Le CPU, synchronisé par son horloge, fonctionne selon des cycles précis, et chaque cycle doit idéalement être exploité pour maximiser les performances. L’objectif est d’exécuter au moins une instruction par cycle, voire davantage dans des architectures multi-cœurs et hyper-threadées.

- Instruction par Cycle : Un cœur logiciel doit être capable d’exécuter une instruction complète par cycle d’horloge.

- Hyper-Threading : Cette technologie permet de simuler plusieurs cœurs logiciels sur un seul cœur matériel. Ainsi, un seul cœur peut gérer deux threads simultanément, augmentant l’efficacité globale en exploitant les temps morts (comme les latences mémoire).

4. Problématique des Latences et des Caches

L’efficacité du CPU dépend de la capacité à minimiser les temps d’attente liés aux accès mémoire :

- Cycle d’instruction : À chaque cycle, le CPU tente d’exécuter une instruction. Si les données nécessaires ne sont pas immédiatement disponibles (manque dans le cache ou attente de la mémoire), cela crée des temps morts.

- Caches Hiérarchiques : Pour pallier cette problématique, les processeurs modernes intègrent une hiérarchie de caches :

- Cache L1 : Directement intégré dans chaque cœur du CPU, extrêmement rapide mais de faible capacité.

- Cache L2 : Plus grand mais légèrement plus lent, partagé ou non entre plusieurs cœurs.

- Cache L3 : Généralement partagé par tous les cœurs du processeur, plus grand mais encore plus lent.

5. Optimisation via le Codage Bas Niveau

Pour exploiter pleinement la puissance des processeurs modernes, les développeurs doivent coder en tenant compte des caractéristiques des caches et des cycles d’horloge :

- Pré-fetching : Charger en avance les données susceptibles d’être utilisées pour les placer dans les caches.

- Minimisation des Cache Miss : Organiser les données pour réduire les probabilités de manquer une donnée dans le cache (cache miss), ce qui forcerait un accès à la RAM.

- Exploitation Maximale des Cœurs : Avec des technologies comme l’Hyper-Threading, l’objectif est de saturer chaque cœur logiciel avec des instructions, en réduisant les temps d’inactivité liés à la latence mémoire.

TLDR

- Rôle des Caches

- Les caches réduisent la latence mémoire en stockant temporairement les données fréquemment ou récemment utilisées.

- Accéder au cache est beaucoup plus rapide qu’à la RAM (ex. 50 cycles d’horloge contre 1000 cycles).

- Mémoire comme Ressource Distante

- Par analogie, le CPU perçoit la RAM comme un entrepôt distant, nécessitant un long trajet pour accéder aux données.

- De même, les caches agissent comme des entrepôts locaux, rapprochant les données nécessaires.

- Exigences de Performance

- L’objectif : une instruction par cycle d’horloge grâce à des caches hiérarchiques et à des technologies comme l'Hyper-Threading (simulant plusieurs cœurs logiciels sur un seul cœur matériel).

Hiérarchie des Caches

- L1 : Ultra rapide, faible capacité, dédié à chaque cœur.

- L2 : Plus grand, partagé ou non, plus lent.

- L3 : Partagé par tous les cœurs, plus grand mais encore plus lent.

Optimisation Bas Niveau

- Pré-fetching : Charger les données en avance dans le cache.

- Réduction des cache miss : Organiser les données pour minimiser les ratés dans le cache.

- Maximiser l’utilisation des cœurs pour réduire les temps d’inactivité dus aux latences.

Les caches permettent au CPU d'atténuer les goulots d’étranglement de la mémoire, optimisant ainsi les performances et exploitant chaque cycle d’horloge.

6. Évolution des Stratégies de Puissance des Processeurs

1. La Fréquence comme Principal Facteur de Puissance (1990-2010)

Au cours des années 1990 et 2000, la fréquence d’horloge était le principal levier pour augmenter la puissance des processeurs. En augmentant la fréquence (mesurée en MHz ou GHz), les processeurs pouvaient exécuter davantage de cycles d’horloge par seconde, ce qui se traduisait par une augmentation du nombre d’instructions exécutées.

- Fréquences croissantes : À cette époque, les sauts de performance étaient marqués par des augmentations significatives, par exemple, passer de 25 MHz à 100 MHz, puis à plusieurs centaines de MHz. Chaque augmentation offrait des gains de performance substantiels.

- Limites physiques : Cependant, en atteignant des fréquences de plusieurs GHz, des problèmes tels que :

- Dissipation thermique : Plus la fréquence est élevée, plus le processeur chauffe, nécessitant des solutions de refroidissement complexes.

- Consommation énergétique : Une fréquence accrue entraîne une consommation électrique exponentielle.

- Loi de diminishing returns : Les gains de performance deviennent moins significatifs.

2. L’Avènement des Architectures Multi-Cœurs

Avec les limites imposées par les hautes fréquences, les fabricants ont adopté une autre stratégie : augmenter le nombre de cœurs.

- Cœurs multiples : Un processeur avec plusieurs cœurs peut exécuter plusieurs instructions simultanément, réparties entre les cœurs. Par exemple :

- Un processeur dual-core exécute deux threads simultanément.

- Un processeur quad-core peut en exécuter quatre, etc.

- Hyper-Threading : Une autre optimisation consiste à simuler plusieurs cœurs logiciels sur un seul cœur matériel, augmentant ainsi la capacité multitâche.

Impact des Limitations Mémoire

1. Le Facteur Limitant : La Mémoire

Même si les processeurs sont devenus beaucoup plus rapides, la mémoire principale reste un facteur limitant majeur :

- Latence mémoire : Les accès à la mémoire principale sont beaucoup plus lents que les cycles du processeur.

- Virtualisation et caches : Les systèmes modernes utilisent des caches et des mécanismes comme la MMU pour réduire l’impact de ces latences.

2. Effets des Changements de Tâche

Chaque fois qu’un processeur change de tâche (changement de processus ou de thread) :

- Les caches doivent être vidés (flushed), ce qui entraîne une perte temporaire de performance.

- Les TLB (Translation Lookaside Buffers) doivent également être actualisés pour refléter les nouveaux espaces d’adressage.

- Cela génère un "effet de hoquet" où le processeur doit reconstruire ses caches pour retrouver des performances optimales.

Optimisation des tâches :

- Les systèmes d’exploitation doivent planifier les tâches en minimisant les changements trop fréquents, pour éviter les surcoûts liés à ces vidages de caches.

Les Interfaces I/O : Un Défi d'Échelle Temporelle

Les périphériques d'entrée/sortie (I/O) comme les disques, les claviers ou les cartes réseau fonctionnent sur des échelles de temps beaucoup plus lentes que le processeur.

- Échelle de temps relative :

- Si accéder à la mémoire principale est perçu comme lent pour le CPU, accéder à un périphérique est encore plus coûteux en cycles d’horloge.

- Les temps d’accès aux périphériques se mesurent en millisecondes, contre des nanosecondes pour la mémoire.

- Rôle des buses : Les interfaces I/O utilisent des buses spécifiques (comme PCIe ou USB) pour communiquer avec le CPU. Ces communications doivent être soigneusement orchestrées pour éviter les goulots d’étranglement.

Un goulot d’étranglement survient lorsqu’une ressource ou un composant d’un système informatique limite les performances globales, en ralentissant le flux des données ou des instructions entre les différents éléments du système. Par analogie, imaginez un tuyau d’arrosage avec une section rétrécie : bien que l’eau puisse circuler rapidement dans les parties larges, le débit global est limité par le point d’étranglement. De la même manière, dans un ordinateur, un composant moins performant peut ralentir l’ensemble du système.

Synchronisation entre le CPU, la Mémoire et les Périphériques : Les Effets de Buffer

1. Les Périphériques I/O et leur Lenteur Relative

Les périphériques d’entrée/sortie (I/O) sont considérablement plus lents que le CPU et la mémoire principale. Cela crée un écart de performance majeur qu’il est nécessaire de compenser pour éviter de ralentir l’ensemble du système.

- Latence importante : Les disques durs, par exemple, ont des temps d’accès mesurés en millisecondes, tandis que les CPU opèrent en nanosecondes.

- Objectif du buffer : Les périphériques utilisent des buffers pour accumuler les données en attente de traitement, permettant une synchronisation efficace avec la mémoire et le CPU.

2. Effets de Cache et Buffers Mémoire

Les buffers et les caches jouent un rôle crucial dans la réduction de la latence entre les différents composants :

- Mémoire côté périphériques (I/O) : Les périphériques utilisent des buffers internes pour accumuler les données avant de les envoyer ou après les avoir reçues. Cela minimise l'impact de leur lenteur sur le système global.

- Mémoire côté CPU : Les caches situés entre le CPU et la RAM réduisent la latence des accès mémoire, en permettant au CPU d’accéder rapidement aux données fréquemment utilisées.

- Magnitude des différences de vitesse :

- Entre le CPU et la RAM, il peut y avoir une différence de vitesse d’un facteur 1000.

- Entre le CPU et les périphériques, cette différence est encore plus importante, atteignant des centaines de milliers dans certains cas.

3. Effets Multiplicatifs et Coordination

L'écart de performance se multiplie lorsqu'on prend en compte les interactions complexes entre les composants :

- Interaction CPU → Mémoire → Périphériques : Le CPU doit non seulement accéder à la mémoire, mais aussi attendre les données des périphériques connectés. Ces deux processus combinés amplifient les délais globaux.

- Rôle de la mémoire comme intermédiaire : La mémoire sert souvent de zone tampon pour transférer les données entre le CPU et les périphériques, réduisant ainsi les interruptions directes.

4. Un Processus Organisé : Lecture et Exécution des Instructions

Le processus d’exécution des instructions suit un schéma bien défini qui inclut la lecture de données et d’instructions en mémoire :

- Lecture des instructions : Les instructions, écrites en langage machine, sont chargées en mémoire et lues par le CPU via le bus d'adresse et le bus de données.

- Lecture des constantes : Les instructions nécessitent souvent de manipuler des données (constantes ou variables) qui sont elles aussi stockées en mémoire.

- Exécution et stockage des résultats : Une fois exécutées, les résultats sont soit stockés dans des registres internes, soit transférés vers la mémoire principale ou les périphériques.

5. Visualisation du Schéma Fonctionnel

Pour comprendre ces interactions, il est essentiel de différencier :

- La logique schématique : Le schéma d’architecture montre les relations statiques entre les composants (CPU, mémoire, périphériques) et leurs interconnexions via les bus.

- Le processus dynamique : Lorsque le système est en fonctionnement, les instructions orchestrent les flux de données entre les composants, activant et désactivant différents chemins et unités fonctionnelles.

6. Conclusion : Une Architecture Optimisée pour les Différences de Fréquence

L’objectif global du système est d’exploiter pleinement les capacités du CPU malgré les écarts de vitesse entre les composants :

- Les caches et buffers permettent de réduire la latence en évitant des accès inutiles aux composants plus lents.

- Les instructions en mémoire assurent une organisation séquentielle du processus, minimisant les interruptions.

- Les bus et contrôleurs synchronisent les échanges entre les différents niveaux de l’architecture, garantissant un flux ordonné et cohérent des données.

Ainsi, bien que les différences de performances soient significatives entre les éléments, une orchestration efficace permet d’en maximiser les capacités.

TLDR

- Fréquence et Puissance (1990-2010)

- Augmenter la fréquence (MHz → GHz) permettait d'exécuter plus d'instructions par seconde.

- Limites physiques : Dissipation thermique, consommation énergétique, et rendement décroissant ont limité cette approche.

- Transition vers les Multi-Cœurs

- Stratégie : Ajouter des cœurs pour exécuter plusieurs instructions simultanément.

- Hyper-Threading : Simule plusieurs cœurs logiciels sur un seul matériel pour optimiser le multitâche.

- Mémoire comme Facteur Limitant

- Latence mémoire : Les cycles d'accès à la RAM sont bien plus lents que ceux du CPU, provoquant des "temps morts".

- Caches et TLB : Réduisent cet impact en optimisant les traductions et en stockant localement les données fréquemment utilisées.

- Latence des Périphériques (I/O)

- Les périphériques (disques, cartes réseau) opèrent à des échelles de temps beaucoup plus lentes.

- Buffers : Réduisent l’impact des différences de vitesse en accumulant les données avant leur traitement.

- Orchestration Systémique

- Les bus synchronisent CPU, mémoire, et périphériques pour maintenir un flux fluide et cohérent.

- Les caches et buffers compensent les disparités de vitesse, maximisant l'efficacité globale du système.

- Conclusion

Les architectures modernes combinent multi-cœurs, optimisations mémoire, et synchronisation des bus pour équilibrer les écarts de vitesse entre les composants, réduisant les goulots d'étranglement et optimisant les performances.

Résumé des fonctions principales d'un processeur

Fonctions principales :

- Exécuter les instructions : Traiter les opérations arithmétiques, logiques et de transfert de données définies par les programmes.

- Accéder à la mémoire :

- Lire les données (constantes, variables) depuis les zones mémoire spécifiées.

- Écrire les résultats dans la mémoire pour un usage futur.

- Gérer les périphériques via les BUS : Assurer la communication avec les périphériques lents (I/O) en orchestrant les échanges via des buffers ou caches pour minimiser la latence.

Composants clés :

- Unité de contrôle (CU) : Décode les instructions et orchestre les différentes opérations en envoyant des signaux de commande.

- ALU (Arithmetic and Logical Unit) : Effectue les calculs arithmétiques (addition, soustraction, etc.) et logiques (comparaisons, ET/OU, etc.).

- Registres internes : Zones de stockage ultra-rapides pour conserver temporairement les données ou instructions en cours de traitement.

- BUS :

- Bus de données : Transfert des valeurs entre le CPU, la mémoire et les périphériques.

- Bus d'adresse : Localisation des données ou instructions dans la mémoire.

- Bus de contrôle : Coordination et synchronisation des opérations.

Ensemble du fonctionnement :

Ces composants interagissent pour permettre au processeur de :

- Lire et écrire des données en mémoire.

- Exécuter des instructions séquentiellement ou parallèlement.

- Communiquer avec les périphériques tout en optimisant les performances grâce aux caches et buffers.